# Leakage Power Reduction in CMOS Logic Circuit Using Various Techniques

Priyanka<sup>1</sup>, Dr. Kiran V<sup>2</sup>

<sup>1</sup>Student, Department of ECE, RV College of Engineering, Bengaluru, India <sup>2</sup>Associate Professor, Department of ECE, RV College of Engineering, Bengaluru, India

Corresponding Author: Priyanka

#### DOI: https://doi.org/10.52403/ijrr.20221113

#### ABSTRACT

Low power nowadays High-power consumption has turned into a crucial design criterion for VLSI an emerging field. When it comes to energy efficiency, high power dissipation is not thought to be beneficial to battery life in the case of battery-powered applications. It reduces the efficiency, dependability, and cooling expenses of battery life. The high-frequency dynamic variation of inputs is heavily influenced by switching and short-circuit leakage power. There are several common methods for reducing the power consumption of circuits. The average power consumption dynamic consists of static and power The consumption consumption. power comparison of LECTOR, LCNT, Stack 0N0FIC, and SAPON of various low-power techniques. These circuits are simulated in the cadence tool.

*Keywords:* LECTOR, LCNT, Stack 0N0FIC, and SAP0N Techniques, cadence tool (90nm).

## **INTRODUCTION**

Digital portable systems are under more and more pressure to be energy efficient in today's technologies. In VLS1 technology [9]. size. power consumption, and Significant design characteristics include propagation delay. But the use of low-power design has grown in importance in device portability in order for VLSI systems to perform well, A serious issue is excessive power use a lot of power Consumption decreases battery life and needs more cooling and packing fees. Many factors affect how much power is used, consisting of operating frequency, transistor count, and the most advancing technology that has an impact. power in excess Consumption causes devices to heat up, reducing their dependability, efficiency, and performance. Simulation of these was done in the cadence tool and tabulated the power consumption by using these techniques.

#### I. POWER CONSUMPTION

The power consumption of the circuit is the sum of Static power and Dynamic power.

A. Dynamic power:

The parasitic capacitor charges and discharges when a toggle is made from 0 to 1 or vice versa. Dynamic consumption results from this charging and discharging. The formula for dynamic power consumption is provided by.

$P = \alpha^* f^* C^* V_{dd}^2$

where,

- $\alpha$  switching activity

- f frequency

- C load capacitance

- $V_{dd}$  supply voltage

- B. Static power leakage:

The sub-threshold channel conductance current and reverse bias P-N junction current are the main causes of leakage power. When the leakage current falls below the threshold voltages, sub-threshold power results. The following elements influence subthreshold leaking,

• Thermal voltage (Vth),

(1)

• Difference between the actual gate voltage (Vg) and threshold voltage (Vt).

The reverse-biased PN junction current is given by

$$\mathbf{I}_{\mathbf{D}} = \mathrm{Is} \left( \mathbf{e}^{\mathbf{V}/\mathbf{Vt}} \mathbf{-1} \right)$$

(2)

# C. Short Circuit Leakage Power:

Dvnamic power consumption is significantly impacted by short circuit leakage [12]. There is a period during the transition when the gates' voltage is between the NMOS and PMOS thresholds, turning on both transistors [1]. Due to the nature of the CM0S architecture [9], power loss results from the formation of a straight conducting line from the voltage source to the ground while both transistors are in the ON state. This power is influenced by the length, incline, and 1-V curve of the transistor loading capacitances.

$$P = I_{mean} * V$$

(3)

# **DESIGN METHODOLOGY**

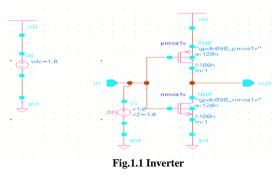

## A. Inverter:

In the conventional CM0S logic inverter, the source terminals of the PM0S transistor and NM0S transistors are connected to Vdd and ground, respectively. The drain terminals are where the output is obtained, and the input is connected to the gate terminals. as shown in Fig. 1.1. If the input is logical high its output will be logic zero and vice versa

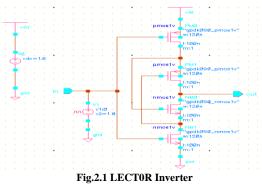

## B. LECTOR:

In this method, leakage-controlled transistor PMOS and NMOS transistors are inserted between logic cells, as shown in Fig. 2.1, with each transistor's gate terminal coupled

to the source of another transistor [3]. Low power consumption is the result of the efficient stacking of transistors between the supply voltage ( $V_{dd}$ ) and GND (ground) [7]. One transistor in the logic circuit remains in the cut-off zone throughout each step of the input cycle, for current flow it provides resistance and lowers power consumption [13].

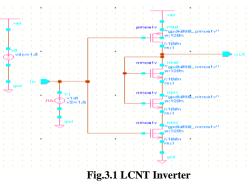

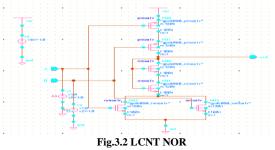

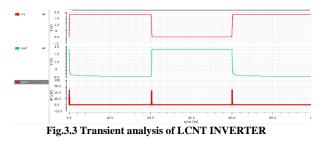

# C. LCNT:

It is also one of the techniques for leakage reduction in which, as illustrated in Fig. 3.1, two leakage-controlled NMOS transistors are added between the logic cells with both of their gate terminals linked to the output node [4]. So, by making the path between the supply voltage ( $V_{dd}$ ) and the GND (ground) more resistant, less power is used. This technique's utility in driven circuits is reduced by the drawback that it cannot pull up or pull down to the precise value.

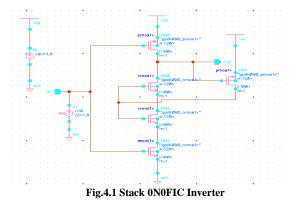

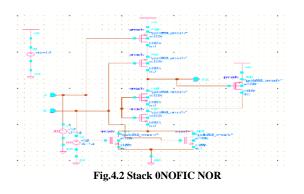

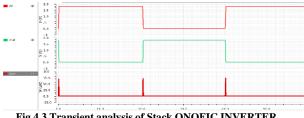

# D. Stack ONOFIC:

The inclusion of a PM0S transistor LCNT circuit is Stack ONOFIC (ON or OFF). The drain terminal of the PM0S transistor is to two NMOS transistors gate terminals [5], the NM0S is series with the logic. The gate

terminal of PMOS connected to the output as shown in Fig. 4.1. The block that was put into the logic is known as the Stack 0N0FIC block [3]. This block presents the lowest ON state hindrance and the highest OFF state hindrance. Low power reduction is achieved in this way.

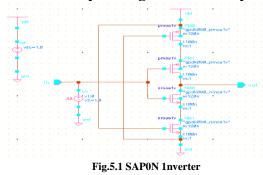

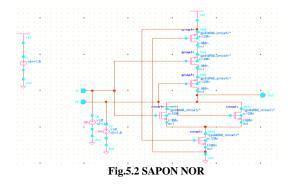

#### E. SAPON:

In this technique the resistance between the supply voltage  $(V_{dd})$  and GND (ground), is by connecting two leakage-control transistors outside the logic. This prevents leakage current from a short circuit during the changeover stage. In addition, it uses CM0S SAP0N transistors connected in series between the supply voltage  $(V_{dd})$  and the GND (ground) to manage the subcurrent during threshold leakage the leveling phase. NMOS and PMOS SAPON Transistors' gate terminals are connected to ground (GND) and Vdd (supply voltage), respectively. According to Fig. 5.1, SAPON PM0S is positioned above the pull-up network, while SAPON NMOS is positioned below the pull-down network. Due to the need to function in an active region, these two SAPON transistors are active during all phases. Consequently, it produces desired results while yet using little electricity.

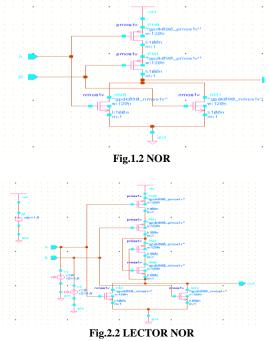

# F. NOR:

A NOR gate is a type of digital logic gate that gives logic high output if all the inputs are 0 and gives logic low output if any one of the inputs is 1. As long as the input voltage is less than the threshold, logic 0 is the output of the NOR. Fig.1.2 Shows the schematic of NOR.

In LECTOR NOR two leakage-controlled transistors of PMOS and NMOS transistors are connected between logic cells, as shown in Fig. 2.2.

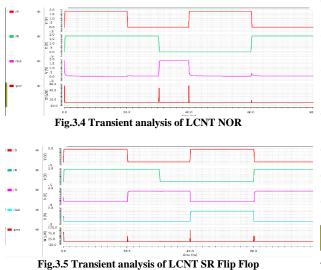

In the LCNT NOR in between the logic cell, two NM0S leakage-controlled transistors are added with both of their gate terminals linked to the Output node as shown in Fig.3.2.

In the Stack, ONOFIC the PMOS transistor, and the drain terminal are connected to two series-connected NMOS transistors and the PMOS gate terminal is connected to the Output node. as shown in Fig. 4.2.

In the SAPON PMOS and NMOS SAPON Transistors' gate terminals are connected to the supply voltage ( $V_{dd}$ ) and the GND (ground), respectively. According to Fig. 5.2, SAPON PMOS is positioned above the pull-up network, while SAPON NMOS is positioned below the pull-down network.

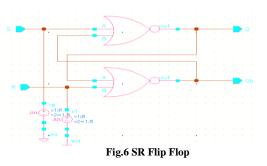

## SR Flip Flop:

The flip-flop has two complementary outputs that are Q and Q and two inputs that are R and S. It's necessary to keep in mind that logic '1' is a dominating input for NOR gates, which means that if any one of its inputs is logic '1' (HIGH), the output will always be logic '0' (LOW), regardless of the other input. By using NOR of different techniques design the SR Flip Flop circuit.

TABLE 3. Truth Table of SR Flip Flop

| S | Q                     | State                    |

|---|-----------------------|--------------------------|

| 0 | Last state            | No change                |

| 1 | 1                     | Set                      |

| 0 | 0                     | Reset                    |

| 1 | Not applied           | Forbidden                |

|   | 8<br>0<br>1<br>0<br>1 | 0 Last state   1 1   0 0 |

## SIMULATION AND RESULT

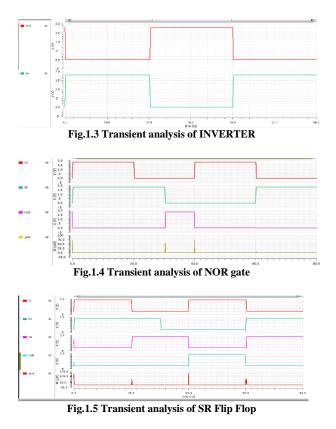

Fig.1.3, 1.4, 1.5 shows the Transient analysis of INVERTER, NOR, and SR Flip Flop respectively.

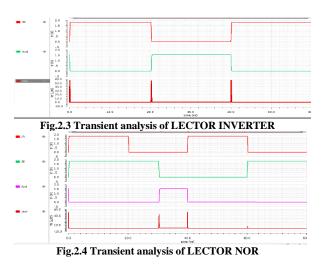

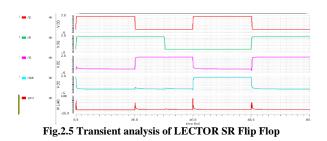

Fig.2.3, 2.4, 2.5 shows the Transient analysis of LECTOR INVERTER, NOR, and SR Flip Flop respectively.

Fig.3.3, 3.4, 3.5 shows the Transient analysis of LCNT INVERTER, NOR, and SR Flip Flop respectively.

Fig.4.5 Transient analysis of Stack ONOFIC SR Flip Flop

Fig.4.3, 4.4, and 4.5 shows the Transient analysis of Stack ONOFIC INVERTER, NOR, and SR Flip Flop respectively.

Fig.3.3, 3.4, 3.5 shows the Transient analysis of SAPON INVERTER, NOR, and SR Flip Flop respectively.

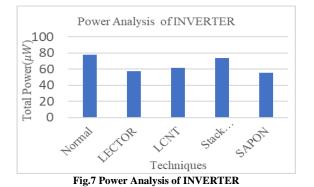

| TABLE 4. FOWER Analysis of INVERTER |            |                       |  |  |

|-------------------------------------|------------|-----------------------|--|--|

| Techniques                          | Number of  | Total Power = Static  |  |  |

|                                     | Transistor | Power + Dynamic Power |  |  |

|                                     |            | <b>(μW</b> )          |  |  |

| Normal                              | 2          | 77.69                 |  |  |

| LECTOR                              | 4          | 57.19                 |  |  |

| LCNT                                | 4          | 61.82                 |  |  |

| Stack                               | 5          | 73.52                 |  |  |

| ONOFIC                              |            |                       |  |  |

| SAPON                               | 4          | 55.34                 |  |  |

TABLE 4. Power Analysis of INVERTER

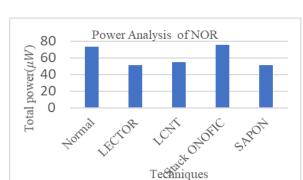

#### TABLE 5. Power Analysis of NOR

| Techniques      | Number of<br>Transistor | Total Power = Static<br>Power + Dynamic Power<br>$(\mu W)$ |

|-----------------|-------------------------|------------------------------------------------------------|

| Normal          | 4                       | 73.25                                                      |

| LECTOR          | 6                       | 51.31                                                      |

| LCNT            | 6                       | 55.02                                                      |

| Stack<br>ONOFIC | 7                       | 75.52                                                      |

| SAPON           | 6                       | 51.02                                                      |

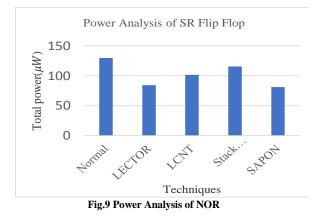

TABLE 6. Power Analysis of SR Flip Flop

| Techniques      | Number of<br>Transistor | Total Power = Static<br>Power + Dynamic Power<br>$(\mu W)$ |

|-----------------|-------------------------|------------------------------------------------------------|

| Normal          | 8                       | 129.85                                                     |

| LECTOR          | 12                      | 84.35                                                      |

| LCNT            | 12                      | 101.65                                                     |

| Stack<br>ONOFIC | 14                      | 115.58                                                     |

| SAPON           | 12                      | 81.18                                                      |

Fig.8 Power Analysis

## **CONCLUSION**

The conventional methodologies were modified in order to develop a reliable lowpower strategy for VLSI in digital systems. For the logic circuit, these techniques are used for low power consumption. Compare to all technique the SAPON techniques gives greater contribution to 10w power, which in turn results in energy savings and improved performance. Since we were able to reduce power consumption in basic logic gates by utilizing SAPON approaches, one can do the same in combinational circuits that are formed from basic gates.

# Acknowledgement: None

# **Conflict of Interest:** None

## **REFERENCES**

- 1. Sainiranjan Muchakayala, Owais Shah, "An Effective Sleep State Approach in Low leakage Power, VLSI Design," International Research Journal of Engineering and Technology, vol.03, May 2016.

- 2. Subrat Mahalik, M.Bhanu Teja, "Leakage Power Reduction in CMOS VLSI," International Journal of Engineering Research & Technology, vol.03, May 2014.

- Chanchal Kumar, Avinash Sharan Mishra, and Vijay Kumar Sharma, "Leakage Power Reduction in CMOS Logic Circuits Using Stack ONOFIC Technique," In Proc. Second International Conference on Intelligent Computing and Control Systems, 2018.

- 4. R. Lorenzo and S. Chaudhury, "LCNT-an approach to minimize leakage power in CMOS integrated circuits. Microsystem

Technologies," vol. 23, no. 9, pp 4245–4253, 2017.

- V. K. Sharma, M. Pattanaik and B. Raj, "ONOFIC approach: low power high speed nanoscale VLSI circuits design," International Journal of Electronics, 2013.

- A. Abdollahi, F. Fallah, and M. Pedram, "Leakage current reduction in CMOS VLSI circuits by input vector control," IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol.12, pp. 140–154, Feb 2004.

- N. Hanchate, and N. Ranganathan, "LECTOR: A technique for leakage reduction in CMOS circuits," IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol.12, pp. 196–205, Feb 2004.

- Jr. Alberto Wiltgen, Kim A. Escobar, André I. Reis, Renato P. Ribas, "Power Consumption Analysis in Static CMOS Gates," Integrated Circuits and Systems Design, Sep 2013.

- A. P. Chandrakasan, S. Sheng and R. W. Brodersen, "Low power CMOS digital design," IEEE J. Solid-State Circuits, vol. 27, pp. 473- 484, Apr 1992.

- 10. Rajesh Yadav, Reetu, Rekha Yadav, "Dynamic power reduction techniques for

CMOS logics using 45nm technology," International Conference on Intelligent Computing and Smart Communication 2019, pp. 1117-1126, Dec 2019.

- 11. Vijay Kumar Sharma, "Design and Simulation of Reliable Low Power CMOS Logic Gates," IETE Journal of Research, Dec 2020.

- 12. Mohammad Moradinezhad Maryan, Majid Amini-Valashani, Seyed Javad Azhari, "A New Circuit-Level Technique for Leakage and Short-Circuit Power Reduction of Static Logic Gates in 22-nm CMOS Technology," Circuits, Systems, and Signal Processing, Mar 2021.

- 13. Narender Hanchate, Nagarajan Ranganathan, "LECTOR: A Technique for Leakage Reduction in CMOS Circuits," IEEE Transaction on Very Large Scale Integration (VLSI) Systems, vol. 12, No. 2, Feb 2004.

How to cite this article: Priyanka, Kiran V. Leakage power reduction in CMOS logic circuit using various techniques. *International Journal of Research and Review*. 2022; 9(11): 79-85. DOI: https://doi.org/10.52403/ijrr.20221113

\*\*\*\*\*